Self-calibrated 10 mbit/s phase modulator with low power fractional PLL architecture

At this week's IEEE International Solid-State Circuits Conference (ISSCC2016), nanoelectronics research center imec and Vrije Universiteit Brussel (VUB) presented a self-calibrated high-speed (10Mbits/s) phase modulator achieving an excellent Error Vector Magnitude (EVM) of -37dB at 10.25 GHz. The modulator is based on a l analog fractional subsampling PLL featuring a world leading -246.6dB Figure of Merit (FOM). It is an attractive solution for phase modulation in highly efficient polar transmitters.

Radio frequency synthesizers are ubiquitous building blocks of today's ever growing networking solutions. Whether for high throughput applications like LTE-Advanced or for sub-mW Internet-of-Things nodes, the phase noise of the RF synthesizer sets a limit to the achievable data rate or to the total radio power consumption, as one can often be traded for the other. On top of that, for efficient spectrum usage, the new standards typically involve higher order modulation schemes. Polar transmitters, using efficient nonlinear power amplifiers might be a good option, but they need highly accurate phase modulators.

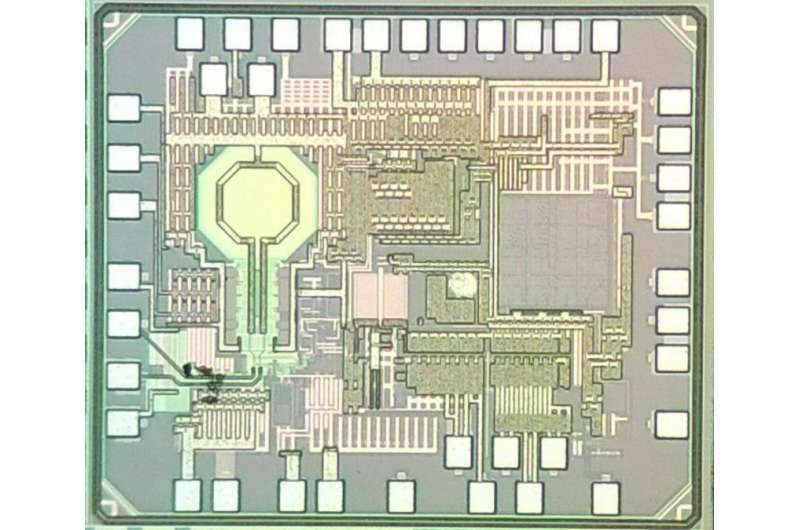

The PLL is built around an analog-based subsampling high-gain phase detector, which enables low-noise operation. The advanced 28nm CMOS technology is exploited to enhance its performance through innovative built-in background self-calibration that corrects all non-idealities of the analog building blocks. Together, these technique ensure a state-of-the-art noise performance resulting in only 176fsec jitter. Similarly, digital phase modulation is implemented, with quasi-ideal performance thanks to background calibration of all non-idealities. Combined with the intrinsic low noise of the PLL, a record EVM better than -37dB is achieved at 10GHz carrier.

These results were presented at ISSCC2016 as paper 9.7 in the High performance wireless session: "N. Markulic et al.; A Self-Calibrated 10Mb/s Phase Modulator with -37.4dB EVM Based on a 10.1-to-12.4GHz, -246.6dB-FOM, Fractional-N Subsampling PLL."

Provided by IMEC