Intel, Micron Sample 3-Bit-Per-Cell NAND Flash Memory on 25-Nanometer Process Technology

Intel and Micron Technology today announced the delivery of 3-bit-per-cell (3bpc) NAND flash memory on 25-nanometer process technology, producing the industry’s highest capacity, smallest NAND device.

The companies have sent initial product samples to select customers. Intel and Micron expect to be in full production by the end of the year.

The new 64-gigabit (Gb) 3bpc on 25nm memory device offers improved cost efficiencies and higher storage capacity for the competitive USB, SD (Secure Digital) flash card and consumer electronics markets. Flash memory is primarily used to store data, photos and other multimedia for use in capturing and transferring data between computing and digital devices such as digital cameras, portable media players, digital camcorders and all types of personal computers. These markets are under constant pressure to provide higher capacities at low prices.

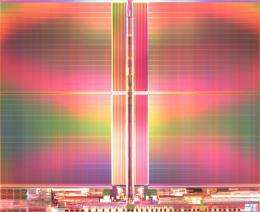

Designed by the IM Flash Technologies (IMFT) NAND flash joint venture, the 64-Gb, or 8 gigabyte (GB), 25nm lithography stores three bits of information per cell, rather than the traditional one bit (single-level cell) or two bits (multi-level cell). The industry also refers to 3bpc as triple-level cell (TLC.)

The device is more than 20 percent smaller than the same capacity of Intel and Micron’s 25nm MLC, which is currently the smallest single 8GB device in production today. Small form-factor flash memory is especially important for consumer end-product flash cards given their intrinsic compact design. The die measures 131mm2 and comes in an industry-standard TSOP package.

“With January’s introduction of the industry’s smallest die size at 25nm, quickly followed by the move to 3-bit-per-cell on 25nm, we continue to gain momentum and offer customers a compelling set of leadership products,” said Tom Rampone, Intel vice president and general manager of Intel NAND Solutions Group. “Intel plans to use the design and manufacturing leadership of IMFT to deliver higher-density, cost-competitive products to our customers based on the new 8GB TLC 25nm NAND device.”

Source: Intel