Learning from sand castles to build future chips

In the United States, data centers already consume two percent of the electricity available with consumption doubling every five years. In theory, at this rate, a supercomputer in the year 2050 will require the entire production of the United States' energy grid.

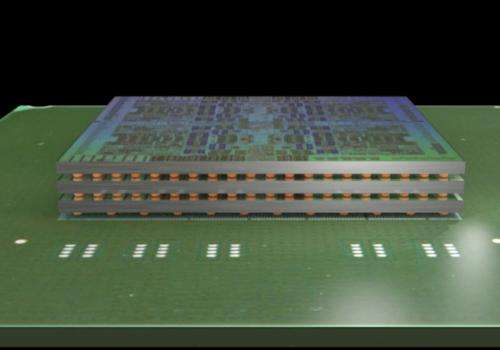

To address this challenge IBM scientists are researching vertically stacked chips, also known as 3D chip stacks. Right now they are developing innovative manufacturing solutions using a natural phenomenon that children around the world appreciate every summer while building sand sculptures—capillary bridging in wet sand.

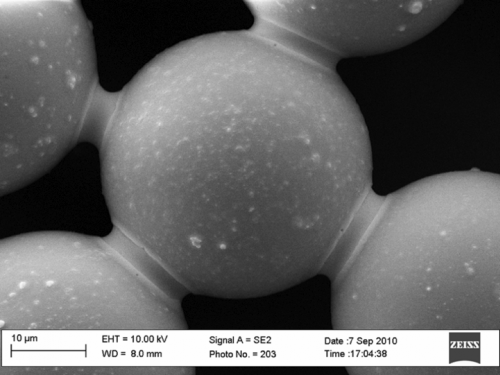

Water trapped between sand grains form so-called capillary bridges. They provide the needed mechanical strength of the sand to create giant works of art. But for electronic packages, they play a slightly different role as they support the formation of novel electrical or thermal interfaces by the self-assembly of nanoparticles.

A 3D chip stack consists of a stack of integrated circuit chips, including vertical electrical interconnects. Between each chip we need to provide hundreds of thousands of periodically arranged connections (that are separated by less than the width of a human hair) to provide the needed communication between the layers. Robust manufacturing processes are key to creating good electrical connections without defects.

IBM scientist Dr. Thomas Brunschwiler has lofty goals for this concept—to create supercomputers that will someday be the size of sugar cubes. But to get there several challenges need to be resolved.

Before heading to the iMAPS conference in San Diego to present his research on novel interconnects by capillary bridging for the first time, he answered a few questions:

Q. What is the main challenge of developing 3D Chip Stacks?

Thomas Brunschwiler: One main challenges for 3D chip stacks is to keep the transistors at temperatures below 80 degrees Celsius, while also considering the multiple chips dissipating heat to a shared heat sink at the backside of the stack. Hence, a low thermal resistance under-fill material is required in the space between the chips formed by the electrical connections. Improvements with traditional capillary under-fills have only resulted in moderate thermal performance.

Q. How are you addressing this challenge?

TB: Our concept is to use the self-assembly of nanoparticles by capillary bridging of liquid between individual micron-sized features between the chips. The nanoparticles in the liquid stay in the fluid during an evaporation process to form so-called "necks" between these micron-sized features. The "necks" could be electrical interconnects between copper pillars, or thermal conductive paths between particle beds filled between the chips by centrifugation. Electrical or thermal "necks" result, depending on the choice of the nanoparticle material.

Q: The concept of necking based on sand castles is fascinatingly simple. How did you come across it?

TB: Our initial investigations with traditional methods were not satisfactory and we ran into several roadblocks. So, we began to think out of the box. We met with our nano-assembly colleagues, including Dr. Heiko Wolf, and he suggested capillary bridging.

We conducted several tests and the concept worked very well right at the start. From the first principle several new ideas were born subsequently.

Q. What type of reaction do you expect at the iMAPS conference?

TB: I could imagine engineers will be fascinated by the simplicity and the performance of the proposed solution. At the same time, they will also be skeptical of a possible robust process for high-volume manufacturing. Up to now, we were performing tests on lab scale samples, to prove the concept. Many more investigations will be needed to yield in a high-end manufacturing process.

On the other hand, the concept could be applicable in other fields, such as front electrodes for solar cells. But as with any science, we need to start small and learn to finally provide a solution.

Consider that in 2006 we had a simple lab concept for a hot water-cooled supercomputer. And in 2012 the fastest supercomputer in Europe, SuperMUC, is based on that design. Progress takes time.

Q. So with all these challenges ahead, what is next?

TB: We will soon start a European wide collaboration with high-tech industries, research institutes and universities to further investigate this technique. So, we need to connect with our partners and begin to scale up the technology.

Provided by IBM Research