April 11, 2011 report

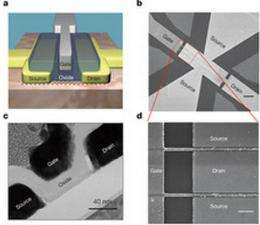

IBM introduces new graphene transistor

(PhysOrg.com) -- In a report published in Nature, Yu-ming Lin and Phaedon Avoris, IBM researchers, have announced the development of a new graphene transistor which is smaller and faster than the one they introduced in February of 2010. This new transistor has a cut-off frequency of 155 GHz, compared to the 100 GHz previous transistor.

Graphene is a flat sheet of carbon which is one atom thick and has the ability to conduct electrons at extremely fast speeds. It is quickly on its way to replace the traditional silicon as the top electronic material for faster transistors.

Graphene devices have been made previously by placing the graphene sheet on top of an insulating substrate, such as silicon dioxide. However, this substrate can degrade the electronic properties of the graphene. However, the team of researchers has found a solution to minimize that.

A diamond-like carbon is placed as the top layer of the substrate on a silicon wafer. The carbon is non-polar dielectric and does not trap or scatter charges as much as the silicon dioxide alone. This new graphene transistor, due to the diamond-like carbon, shows excellent stability in temperature changes, including extremely cold temperatures like that in space.

These new high-frequency transistors are being targeted to applications primarily in communications such as mobile phones, internet, and radar.

The manufacturing of these new graphene transistors can be accomplished utilizing technologies already in place for standard silicon devices, which means commercial production of these transistors could begin at any time.

The transistor development was part of an ongoing research project IBM is doing for the U.S. Department of Defense’s DARPA (Defense Advanced Research Projects Agency) program. The military is looking to this research to help in the development of high-performance radio frequency transistors.

More information: High-frequency, scaled graphene transistors on diamond-like carbon, Nature, 472, 74–78 (07 April 2011) doi:10.1038/nature09979

© 2010 PhysOrg.com