September 11, 2023 feature

This article has been reviewed according to Science X's editorial process and policies. Editors have highlighted the following attributes while ensuring the content's credibility:

fact-checked

peer-reviewed publication

trusted source

proofread

A physics-based Ising solver based on standard CMOS technology

Quantum computers, systems that perform computations by exploiting quantum mechanics phenomena, could help to efficiently tackle several complex tasks, including so-called combinatorial optimization problems. These are problems that entail identifying the optimal combination of variables among several options and under a series of constraints.

Quantum computers that can tackle these problems should be based on reliable hardware systems, which have an intricate all-to-all node connectivity. This connectivity ultimately allows graphs representing arbitrary dimensions of a problem to be directly mapped onto the computer hardware.

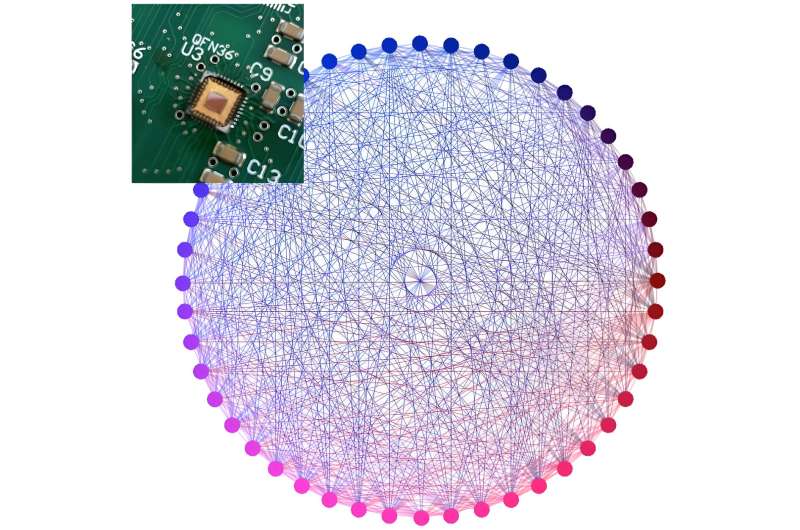

Researchers at University of Minnesota recently developed a new electronic device based on standard complementary metal oxide semiconductor (CMOS) technology that could support this crucial mapping process. This device, introduced in a paper in Nature Electronics, is a physics-based Ising solver comprised of coupled ring oscillators and an all-to-all node connected architecture.

"Building an all-to-all connected hardware where each node (i.e., oscillator) can 'talk' to all other nodes is extremely challenging; as the number of coupled nodes (N) increases, the number of connections per node increases by ~N2. This results in a quadratically increasing electrical loading and hardware overhead for each node which makes the coupling less efficient and less uniform," Chris Kim, one of the researchers who carried out the study, told Phys.org.

"Previous works, including our own, focused on locally connected architecture where each node could talk to only a handful (e.g., <10) of nearby nodes. An all-to-all architecture is ideal as problems can be directly mapped to the hardware but up until this point, there was no elegant way to achieve this."

The Ising solver created by Kim and his colleagues has an all-to-all architecture containing 48 spins and a highly uniform coupling circuit. Horizontal oscillator in the device are closely coupled to vertical oscillators, creating pairs of horizontal-vertical oscillators that intersect with other pairs to form a crossbar array.

"The basic idea behind our Ising solver is to propagate an oscillating signal in both horizontal and vertical directions in a way that node i and node j intersect each other throughout a crossbar array," Kim explained. "By placing a coupler circuit at each intersection, we can build a circuit array where each node signal talks to all other node signals. Despite the oscillating signals being phase shifted throughout the array, coupling between two nodes occurs in a way that accounts for the shifted phases which is why the proposed design finds a competitive solution. "

The researchers evaluated their Ising solver in a series of tests, where they used it to perform various statistical operations, gathering measurements for problems of varying sizes and with different graph densities. Their results were promising, as graphs representing the dimensions of these problems could be effectively mapped onto their chip.

"With our new approach, we can directly map a problem graph with up to 48 nodes to the solver hardware," Kim said. "This is a significant improvement over previous designs; for instance, a King's graph-based hardware was demonstrated by several groups including ours, but each node could only talk to eight other neighbors."

In the future, the chip introduced by Kim and his colleagues could inform the creation of further Ising solvers and devices that can map intricate problem graphs. This could ultimately help to further improve the ability of quantum computers to solve combinatorial optimization problems, facilitating their real-world deployment.

"Since the problems we want to solve are much larger than a single hardware instance, we will have to find a way to decompose and recompose sub-problems without sacrificing the solution accuracy," Kim added.

"Another topic of interest is comparing the solution quality of our hardware against existing optimization algorithms such as simulated annealing or tabu search. Finally, we will have to find more systematic ways to formulate a problem to coupling weights; we cannot democratize this computing approach if a human expert is required at every step of the computation."

More information: Hao Lo et al, An Ising solver chip based on coupled ring oscillators with a 48-node all-to-all connected array architecture, Nature Electronics (2023). DOI: 10.1038/s41928-023-01021-y

Journal information: Nature Electronics

© 2023 Science X Network