August 8, 2014 feature

Researchers build first 3D magnetic logic gate

(Phys.org) —The integrated circuits in virtually every computer today are built exclusively from transistors. But as researchers are constantly trying to improve the density of circuits on a chip, they are looking at alternative ways to build circuits. One alternative method uses nano-sized magnets, in which the magnets possess two stable magnetic states that represent the logic states "0" and "1."

Until now, nanomagnetic logic (NML) has been implemented only in two dimensions. Now for the first time, a new study has demonstrated a 3D programmable magnetic logic gate, where the magnets are arranged in a 3D manner. In comparison to the 2D gate, the 3D arrangement of the magnets allows for an increase in the field interaction between neighboring magnets and offers higher integration densities.

The researchers, Irina Eichwald, et al., at the Technical University of Munich in Munich, Germany; and the University of Notre Dame in Notre Dame, Indiana, US, have published their paper on the 3D magnetic logic gate in a recent issue of Nanotechnology.

"We showed for the first time that magnetic field coupling can be exploited in all three dimensions in order to realize magnetic logic computing circuitry, and therefore paves the way for new technologies, where high integration densities combined with low power consumption can be achieved," Eichwald told Phys.org.

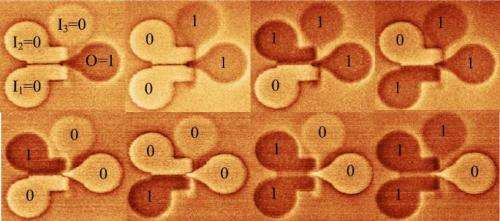

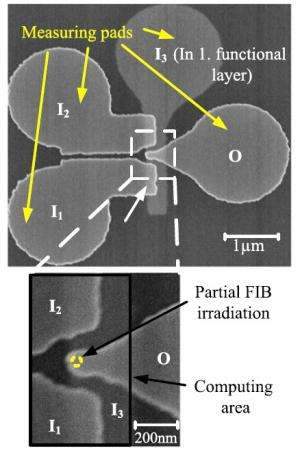

The 3D magnetic logic gate consists of three input magnets that influence the magnetic state of one output magnet. To prepare the output magnet, the researchers used a focused ion beam to irradiate a 40 x 40-nm area of the magnet to destroy its crystalline structure, creating a domain wall. When the magnetic fields from the three input magnets are placed within 100 nm of the irradiated spot, the domain wall's magnetic state can be controlled. As a result, the output magnet can be switched between the "0" and "1" states.

One important feature of the 3D magnetic logic gate is that one of the input magnets is arranged in an extra layer in comparison to 2D magnetic logic gates. Adding a third dimension enhances the amount of magnetic area surrounding the output magnet by 1/3, and also increases the influence of each input magnet by 1/6. These stronger magnetic effects reduce the error rate and improve the functionality of the gate. The input magnet in the third dimension also programs the gate to operate as either a NOR or NAND gate.

NML has several potential advantages compared to transistors. One is that there is no need for electrical wiring or interconnects because the computation is performed entirely by magnetic interactions between neighboring magnets. NML also operates with low power consumption, which in turn enables the combination of logic and memory functionality in a single device.

There is also the advantage of high densities using NML, which is possible in part due to the small size of the 3D magnetic gates (here, about 700 x 550 nm). Although high densities lead to the problem of stray magnetic fields interfering with magnets other than their nearest neighbors, the researchers note that previous research has already begun discussing and proposing solutions to these problems. Overall, NML could have a variety of applications.

"The main aspect of 3D nanomagnetic logic is that you can build up circuits, in which a huge number of the computing processes is done simultaneously (the keyword is systolic architecture), while the power consumption is kept at a minimum (as you only need to generate a global magnetic field and then you can clock the whole circuitry)," Eichwald said. "Applications are digital filtering, decoding and cryptography. Here all computing processes should be done by magnets."

The results here pave the way for the development of other 3D architectures of NML circuits in the future.

"The future research plans are to investigate a 3D full adder structure, with the lowest possible number of magnets and the smallest area consumption," Eichwald said.

More information: Irina Eichwald, et al. "Majority logic gate for 3D magnetic computing." Nanotechnology 25 (2014) 335202 (8pp). DOI: 10.1088/0957-4484/25/33/335202

Journal information: Nanotechnology

© 2014 Phys.org