## Designer-defect mediated clamping of ferroelectric domain walls for more stable nanoelectronics

January 20 2020

Co-author Dr Daniel Sando preparing materials for study at UNSW. Credit: FLEET

A UNSW study published today in *Nature Communications* presents an exciting step towards domain-wall nanoelectronics: a novel form of future electronics based on nano-scale conduction paths, and which could allow for extremely dense memory storage.

FLEET researchers at the UNSW School of Materials Science and Engineering have made an important step in solving the technology's primary long-standing challenge of information stability.

Domain walls are "atomically sharp" <u>topological defects</u> separating regions of uniform <u>polarisation</u> in <u>ferroelectric materials</u>.

Domain walls in ferroelectrics possess fascinating properties, and are considered separate entities with properties that are dramatically different from the parent bulk ferroic material.

These properties are brought about by changes in structure, symmetry and chemistry confined within the wall.

"This is the fundamental starting point underpinning <u>domain</u> wall nanoelectronics," says study author Prof Jan Seidel.

The "switching" property of ferroelectric materials makes them a popular candidate for low-voltage nanoelectronics. In a ferroelectric transistor, distinct polarization states would represent the computational zero and one states of binary systems.

However, the stability of that stored polarization information has proven to be a challenge in application of the technology to <u>data storage</u>, especially for very small nanoscale domain sizes, which are desired for high storage densities.

Ferroelectric materials can be considered the electrical equivalent of a permanent magnet, possessing a spontaneous polarisation. This polarisation is 'switchable' by an electric field. Credit: FLEET

"The polarization state in ferroelectric materials decays typically within days to a few weeks, which would mean information storage failure in any domain-wall data storage system," says author Prof Nagy Valanoor.

The period of time that information can be stored in ferroelectric materials, ie the stability of the stored polarization information, is thus a key performance feature.

To date, this long-standing issue of information instability has been one of the main limitations on the technology's application.

The study investigates the ferroelectric material BiFeO3 (BFO) with specially introduced designer defects in thin films. These designer defects can clamp down <u>domain walls</u> in the material, effectively preventing the ferroelectric domain relaxation process that drives information loss.

"We used a 'defect engineering' method to design and fabricate a special

BFO thin film that is not susceptible to retention loss over time," says lead author Dr. Daniel Sando.

Pinning of domain walls is thus the main factor used to engineer very long polarization retention.

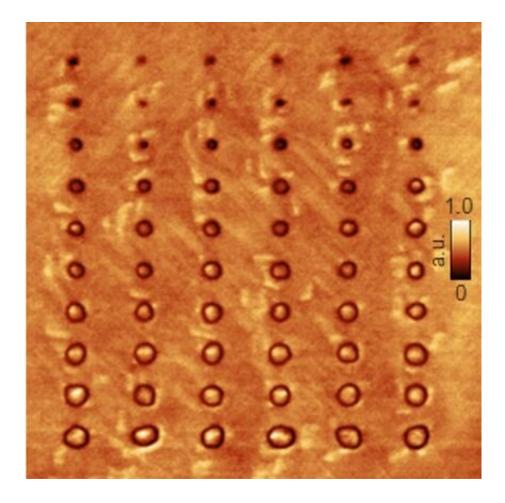

Voltage-dependent domain formation. Credit: FLEET

"The novelty of this new research lies in precisely-controlled pinning of the domain wall, which allowed us to realize superior polarization retention," says lead author Dawei Zhang.

The research provides critical new thinking and concepts for domainwall based nanoelectronics for non-volatile data <u>storage</u> and logic device architectures.

In addition the mixed phase BFO–LAO system is a fertile ground for other intriguing <u>physical properties</u>, including piezoelectric response, field-induced strain, electrochromic effects, magnetic moments, electrical conductivity and mechanical properties.

**More information:** Dawei Zhang et al. Superior polarization retention through engineered domain wall pinning, *Nature Communications* (2020). DOI: 10.1038/s41467-019-14250-7

## Provided by FLEET

Citation: Designer-defect mediated clamping of ferroelectric domain walls for more stable nanoelectronics (2020, January 20) retrieved 28 April 2024 from <u>https://phys.org/news/2020-01-designer-defect-clamping-ferroelectric-domain-walls.html</u>

This document is subject to copyright. Apart from any fair dealing for the purpose of private study or research, no part may be reproduced without the written permission. The content is provided for information purposes only.